### **Masterarbeit**

# Prototypische Treiberentwicklung zur Ansteuerung von Peripherie mittels One-Wire-zu-l<sup>2</sup>C-Brücke für ein eingebettetes Linux-System

#### **Rico Goldhardt**

Matrikel 39389 Seminargruppe 221079/KVZ

Westsächsische Hochschule Zwickau Fakultät Physikalische Technik / Informatik Studiengang Informatik

**Betreuer** M.Sc. Andreas Dinter

SYS TEC electronic AG

**Gutachter** Prof. Dr. Frank Grimm

Prof. Dr. Wolfgang Golubski

Westsächsische Hochschule Zwickau

### Selbstständigkeitserklärung

| Hiermit versichere ich, dass ich die vorliegende Arbeit in allen Teilen selbstständig angefertigt und keine anderen als die in der Arbeit angegebenen Quellen und Hilfsmittel benutzt habe, und dass die Arbeit in gleicher oder ähnlicher Form in noch keiner anderen Prüfung vorgelegen hat. Mir ist bewusst, dass ich Autor/in der | V |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| vorliegenden Arbeit bin und volle Verantwortung für den Text trage.<br>Ich erkläre, dass ich wörtlich oder sinngemäß aus anderen Werken – dazu gehören<br>auch Internetquellen – übernommene Inhalte als solche kenntlich gemacht und die                                                                                             | Ø |

| entsprechenden Quellen angegeben habe.<br>Mir ist bewusst, dass meine Arbeit auf Plagiate überprüft werden kann. Mir ist bekannt, dass es sich bei der Abgabe eines Plagiats um ein schweres akademisches Fehlverhalten handelt und dass Täuschungen nach der für mich gültigen Prüfungsordnung geahndet werden.                      | Ø |

| Zusätzlich versichere ich, dass ich auf künstlicher Intelligenz (KI) basierende<br>Werkzeuge nur in Absprache mit den Prüfern verwendet habe. Dabei stand meine<br>eigene geistige Leistung im Vordergrund, und ich habe jederzeit den Prozess<br>steuernd bearbeitet.                                                                | V |

| Diese Werkzeuge habe ich im Quellenverzeichnis in der Rubrik "Übersicht verwendeter Hilfsmittel" mit ihrem Produktnamen und einer Übersicht des im Rahmen dieser Prüfungs-/Studienarbeit genutzten Funktionsumfangs unter Angabe der Textstelle in der Arbeit vollständig aufgeführt.                                                 | V |

| Ich versichere, dass ich keine KI-basierten Tools verwendet habe, deren Nutzung die Prüfer explizit schriftlich ausgeschlossen haben. Ich bin mir bewusst, dass die Verwendung von Texten oder anderen Inhalten und Produkten, die durch KI-basierte Tools generiert wurden, keine Garantie für deren Qualität darstellt.             | Ø |

| Ich verantworte die Übernahme jeglicher von mir verwendeter maschinell generierter Passagen vollumfänglich selbst und trage die Verantwortung für eventuell durch die KI generierte fehlerhafte oder verzerrte Inhalte, fehlerhafte Referenzen, Verstöße gegen das Datenschutz- und Urheberrecht oder Plagiate.                       | V |

|                                                                                                                                                                                                                                                                                                                                       |   |

Reichenbach, 01.04.2025

Ort, Datum Unterschrift

### **Abstract**

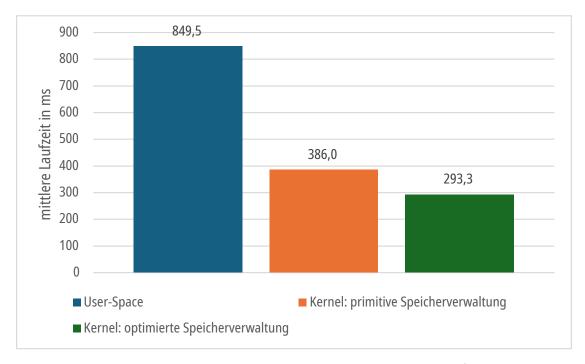

Ziel der vorliegenden Arbeit ist die Entwicklung eines Linux-Treibers für einen Chip, welcher einen I²C-Bus über den One-Wire-Bus bereitstellt und Befehle in einem Sequenzer speichern kann. Dazu werden Anforderungen gestellt, welche sich aus der Projektspezifikation ableiten. Mögliche Implementierungen werden zunächst theoretisch verglichen und anschließend als Bibliothek und Kernel-Treiber implementiert. Bei der Implementierung des Treibers werden dabei zwei Varianten — mit und ohne optimierte Allokationslogik des Sequenzer-Speichers — unterschieden. Die Bibliothek und die beiden Konfigurationen des Treibers werden hinsichtlich ihrer Laufzeit empirisch betrachtet und verglichen. Außerdem wird der Erfüllungsgrad der Anforderungen durch die Treiber-Implementierung bewertet. Im Ergebnis zeigt sich, dass die Implementierung als Kernel-Treiber mit optimierter Speicher-Allokationslogik einen deutlichen Vorteil in der Laufzeit aufweist.

# **Danksagung**

Diese Masterarbeit wurde bei der SYS TEC electronic AG im Unternehmen angefertigt. Das Unternehmen ist Dienstleister zur Entwicklung und Fertigung individueller Elektronik-Lösungen und Embedded-Software.

Ich bedanke mich herzlich bei der SYS TEC electronic AG und allen beteiligten Kolleginnen und Kollegen für die Möglichkeit, diese Arbeit im Unternehmen anzufertigen und die fachliche Unterstützung. Besonderer Dank gilt M. Sc. Andreas Dinter, der diese Arbeit von der Konzeption bis zum Endergebnis betreut, stets konstruktiv Kritik geübt und fachlich unterstützt hat.

Vielen Dank auch an Dr.-Ing. André Werner, für die Unterstützung bei der Einhaltung von Kernel-Coding-Richtlinien durch Code-Reviews, und Dipl.-Inf. Daniel Krüger für die fachliche Expertise.

# **Inhaltsverzeichnis**

| Inl | haltsv | erzeicl/            | hnis                                        | l  |

|-----|--------|---------------------|---------------------------------------------|----|

| ΑŁ  | kürz   | ungsve              | rzeichnis                                   | IV |

| Gl  | ossar  | r                   |                                             | ٧  |

| 1   | Einle  | eitung              |                                             | 1  |

| 2   | Grui   | ndlager             | 1                                           | 3  |

|     | 2.1    | Stand               | der Forschung                               | 3  |

|     | 2.2    | Linux               | im Überblick                                | 4  |

|     | 2.3    | Termi               | nologie                                     | 6  |

|     | 2.4    | One-W               | /ire im Überblick                           | 7  |

|     |        | 2.4.1               | Aufbau eines One-Wire-Netzes                | 8  |

|     |        | 2.4.2               | Ablauf der One-Wire-Kommunikation           | 9  |

|     |        | 2.4.3               | Zyklische Redundanzprüfung (CRC)            | 12 |

|     | 2.5    | I <sup>2</sup> C im | Überblick                                   | 13 |

|     | 2.6    | DS28E               | E18 One-Wire-zu-I <sup>2</sup> C/SPI-Bridge | 14 |

|     |        | 2.6.1               | Kommunikation mit dem DS28E18               | 15 |

| 3   | One    | -Wire u             | nd I <sup>2</sup> C unter Linux             | 19 |

|     | 3.1    | W1-Su               | bsystem: Das Kernel One-Wire-Subsystem      | 19 |

|     | 3.2    | I2C-Su              | ıbsystem                                    | 21 |

| 4 | Kon | zeption | l                                              | 23 |

|---|-----|---------|------------------------------------------------|----|

|   | 4.1 | Besch   | reibung Anwendungsfall / Versuchsaufbau        | 23 |

|   | 4.2 | Zielste | ellung                                         | 24 |

|   | 4.3 | Abgre   | nzung                                          | 26 |

|   | 4.4 | Möglid  | che Implementierungen                          | 26 |

|   |     | 4.4.1   | Implementierung im User-Space                  | 26 |

|   |     | 4.4.2   | Implementierung im Kernel                      | 27 |

|   | 4.5 | Bewer   | tung und Schlussfolgerungen                    | 28 |

| 5 | lmp | lementi | ierung im User-Space                           | 30 |

|   | 5.1 | API De  | esign                                          | 30 |

|   |     | 5.1.1   | One-Wire-Master                                | 31 |

|   |     | 5.1.2   | One-Wire-Slaves                                | 33 |

|   | 5.2 | Limitie | erungen                                        | 33 |

| 6 | lmp | lementi | ierung im Kernel                               | 36 |

|   | 6.1 | Vorge   | hensplan                                       | 36 |

|   | 6.2 | Definit | tion of Done                                   | 37 |

|   | 6.3 | Besch   | reibung der Vorgehensweise                     | 37 |

|   |     | 6.3.1   | Debugging                                      | 37 |

|   |     | 6.3.2   | Implementierung der Grundfunktionen            | 38 |

|   |     | 6.3.3   | Optimierte Sequenzer Speicher-Allokationslogik | 47 |

|   | 6.4 | Proble  | eme bei der Implementierung                    | 51 |

| 7 | Aus | wertun  | g der Ergebnisse                               | 53 |

|   | 7.1 | Bewer   | tung des Kernel-Treibers                       | 53 |

|   |     | 7.1.1   | Erfüllung der Kriterien                        | 53 |

|   |     | 7.1.2   | Zuverlässigkeit                                | 55 |

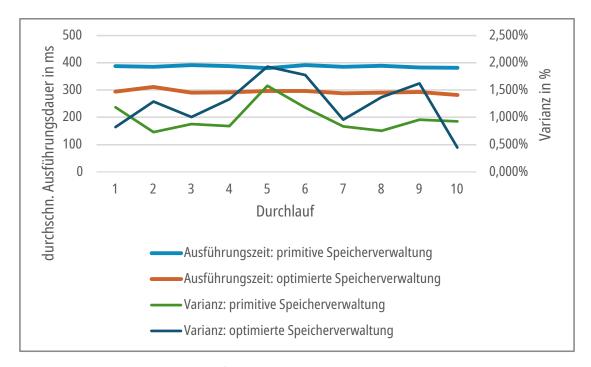

|                          |                         | 7.1.3 Performanzauswirkung der Speicher-Allokationslogik | 56 |  |  |  |

|--------------------------|-------------------------|----------------------------------------------------------|----|--|--|--|

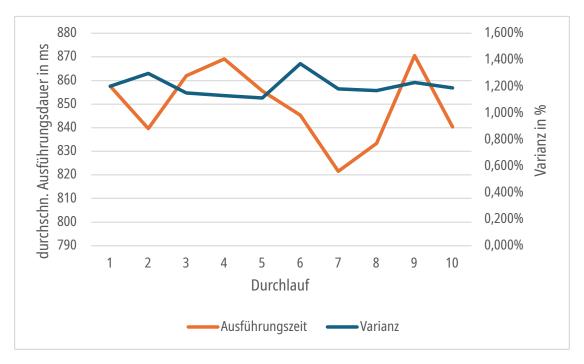

|                          | 7.2                     | Vergleich mit der User-Space Implementierung             |    |  |  |  |

|                          | 7.3                     | Vergleich der Ergebnisse                                 | 60 |  |  |  |

| _                        | 17                      |                                                          |    |  |  |  |

| 8                        | Kriti                   | sche Diskussion                                          | 61 |  |  |  |

|                          | 8.1                     | Stärken der Methode                                      | 61 |  |  |  |

|                          | 8.2                     | Schwächen und Limitationen                               | 61 |  |  |  |

|                          | 8.3                     | Mögliche Verbesserungen                                  | 62 |  |  |  |

| 9                        | Zusa                    | ammenfassung                                             | 63 |  |  |  |

| 10                       | 10 Ausblick 64          |                                                          |    |  |  |  |

| Literaturverzeichnis 65  |                         |                                                          |    |  |  |  |

| Abbildungsverzeichnis 71 |                         |                                                          |    |  |  |  |

| Tabellenverzeichnis 72   |                         |                                                          |    |  |  |  |

| Οιι                      | Quellcodeverzeichnis 73 |                                                          |    |  |  |  |

# Abkürzungsverzeichnis

#### **FPGA**

Field Programmable Gate Array. siehe Glossar: Field Programmable Gate Array

#### LSb

Least Significant Bit. siehe Glossar: Least Significant Bit

#### **MSb**

Most Significant Bit. siehe Glossar: Most Significant Bit

#### **NACK**

Not Acknowledged, auch NAK. siehe Glossar: NACK Paket

#### **POR**

Power-On-Reset. siehe Glossar: Power-On-Reset

#### **SRAM**

Static random-access memory. siehe Glossar: Static random-access memory

#### **VM**

virtuelle Maschine.

## **Glossar**

#### **Bit-Banging**

Bit-Banging ist die Emulation einer seriellen Schnittstelle (z.B. I<sup>2</sup>C, SPI) mittels Software über allgemeine Ein- und Ausgabeports (z.B. GPIO) [Anaa].

#### **EEPROM**

Electrically Erasable Programmable Read-Only Memory. Nicht-flüchtiger Speichertyp, der elektronisch gelöscht und byteweise programmiert werden kann [HEI].

#### Field Programmable Gate Array

Universeller Logikbaustein, der vom Benutzer zur Ausführung verschiedener, komplexer Logikfunktionen verwendet werden kann. [Anab].

#### **Least Significant Bit**

Das niederwertigste Bit einer Bitfolge.

#### **Mainline Linux-Kernel**

Unmodifizierte Kernel-Version von kernel.org. Es ist die Kernel-Version, in der neue Funktionen zuerst als "Stable Release" eingeführt werden. Sie bildet die Grundlage für die meisten Kernel-Ableger.

#### **Most Significant Bit**

Das höchstwertigste Bit einer Bitfolge.

#### **NACK Paket**

Not Acknowledged, auch NAK; Paket, mit dem ein Empfänger Daten, beispielsweise wegen Inkonsistenzen, ablehnt. In der Regel gefolgt von einer erneuten Übertragung der Nachricht, um Übertragungsfehler zu korrigieren.

#### Netzwerkgewicht

Die Gesamtlänge aller Kabel in einem One-Wire-Netz [Ana01b].

#### **Netzwerkradius**

Die Entfernung vom Master zum am weitesten entfernten Slave in einem One-Wire-Netz [Ana01b].

#### One-Wire-Gerätefamilie

Gruppe von One-Wire-Geräten, welche den gleichen Family Code besitzen. Family Codes beschreiben den Typ des Geräts.

#### Power-On-Reset

Das Gerät befindet sich beim ersten Einschalten nach einem Spannungsverlust in einem definierten Ausgangszustand.

#### Reflexion

"Reflexionen entstehen an Koppelstellen von Komponenten [...]. Bei der Reflexion wird ein Signalteil von dieser impedanzabhängigen Stoßstelle reflektiert und überlagert das Originalsignal." [Lip02] Reflexionen können dadurch die Kommunikation beeinträchtigen.

#### relevante Stelle

Stellen, die zum Wert der Bitfolge beitragen. Null-Bits in den **MSb** werden abgeschnitten.

#### **ROM-ID**

"Read-Only-Memory ID". 64-Bit Nummer, mit der alle One-Wire-Geräte eindeutig identifiziert werden können. Sie besteht aus 8-Bit Family-Code, welcher die **One-Wire-Gerätefamilie** identifiziert, einer 48-Bit Seriennummer und 8-Bit Prüfziffer (CRC-8).

#### Slice

Ansicht auf eine zusammenhängende (Sub-) Sequenz im Speicher mit dynamischer Größe [vgl. rus].

#### Static random-access memory

Flüchtiger Speichertyp, welcher kein periodisches Signal zur Auffrischung (Refresh) benötigt um Daten beizubehalten [Anad].

#### sysfs

Pseudo-Dateisystem unter Linux, welches nutzerseitige Schnittstellen zu Kernel-Datenstrukturen bereitstellt. Die Dateien im sysfs stellen Informationen über Geräte, Kernelmodule, Dateisysteme und andere Kernelkomponenten bereit. Der Einhängepunkt liegt üblicherweise unter /sys [Ker24].

#### Trait

Sprachelement in Rust, ähnlich Interfaces in Java.

Möglichkeit notwendige Funktionalitäten zu definieren, welcher ein Typ bereitstellen muss. Traits erlauben Typen, Zusicherungen über bestimmte Verhalten zu treffen [vgl. rus] .

#### Twisted-Pair-Kabel

Kabel, bei dem Paare von Adern miteinander verdrillt sind. Dadurch werden Störeinflüsse durch wechselnde magnetische Felder gemindert [Ele].

#### udev

userspace /dev. User-Space System für Event-Handling bei der Zustandsänderung von Peripheriegeräten (zum Beispiel Hot-Plug). Außerdem verwaltet udev Referenzen auf Geräte-Nodes im Verzeichnis /dev/ [arc25].

# 1. Einleitung

Im Rahmen eines Kundenprojekts entwickelt die SYS TEC electronic AG ein auf Yocto-Linux basierendes Steuergerät zur Anlagensteuerung und -überwachung. Auf diesem wird speziell angefertigte Software, sowie ein Web-Frontend zur Administration ausgeführt. Das Gesamtsystem besteht aus weiteren Komponenten mit diversen Sensoren, Aktoren und Softwarekomponenten, welche mittels CAN-Bus untereinander und mit dem Steuergerät verbunden sind. Eine weitere zentrale Aufgabe des Steuergeräts ist die klimatische Überwachung in und im Umfeld von verteilten Schaltschränken. Dazu verfügt das Steuergerät über eine One-Wire-Schnittstelle, mittels derer externe Sensoren durch RJ-45 terminierter Netzwerkkabel zur Laufzeit angeschlossen werden können. One-Wire ist ein Feldbus, welcher insbesondere aufgrund geringer Kosten bei hoher Zuverlässigkeit eingesetzt wird. Die Projektspezifikation legt fest, dass bis zu zwanzig One-Wire-Geräte gleichzeitig am System angeschlossen werden können. Dazu zählen unter anderem Temperatur- und Feuchtigkeitssensoren, deren Messwerte mit einer Frequenz von 10 Hz durch das Steuergerät erfasst werden sollen. [Ana08]

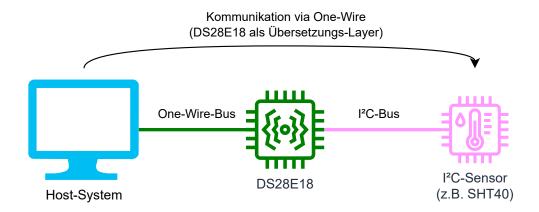

Der Katalog verfügbarer One-Wire-Sensoren ist weitreichend und umfasst verschiedene Gerätearten wie **EEPROM**-Speichermodule, Programmierte Ein- und Ausgänge (PIO), Zeitmesser und Temperatursensoren. Jedoch bietet *Analog Devices*, der Lizenzhaber der One-Wire-Technologie, keine Sensoren zum Messen der Luftfeuchtigkeit an. Um die Anforderung dennoch zu erfüllen, wurde sich für den Einsatz eines SHT40 Sensors entschieden, der gleichzeitig als Sensor für Luftfeuchtigkeit und Temperatur eingesetzt werden kann. Dabei waren die Erfüllung der spezifizierten Messtoleranzen und die Kosten ausschlaggebend für die Entscheidung. Angesteuert wird die SHT4x Sensorfamilie über I²C, ein serielles Protokoll zur Kommunikation zwischen Komponenten. Genauer wird später in Abschnitt 2.5 - I²C im Überblick auf das Protokoll eingegangen. Um diesen Sensor dennoch per One-Wire verwenden zu können, kommt eine sogenannte One-Wire-zu-I²C-Brücke (nachfolgend Bridge) zum Einsatz. Diese kann als I²C-Controller agieren und somit einen I²C-Bus-Interface bereitstellen, während sie gleichzeitig ein One-Wire-Slave ist. Über die One-Wire-Schnittstelle kann sie mit

einem Steuergerät, zum Beispiel einem Linux-Rechner, verbunden werden. Die Kommunikation mit Geräten auf dem I<sup>2</sup>C-Bus wird über die Bridge mittels One-Wire-Befehlen gesteuert. [Anac]

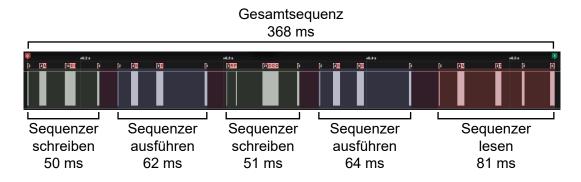

Im Rahmen der weiteren Projektplanung wurde sich dafür entschieden, als One-Wire-zu-l<sup>2</sup>C-Brücke Chips des Typs DS28E18 zu verwenden. Diese verfügen über eine Schnittstelle, um als I2C-Controller oder SPI-Controller zu agieren und mit Geräten an diesem Bus über One-Wire interagieren zu können. Im Folgenden wird auf die gemeinsame Nennung von I2C und SPI im Kontext des DS28E18 verzichtet, da in dieser Arbeit lediglich die I<sup>2</sup>C-Funktionalität des Chips eingesetzt wird. Im Gegensatz zu Chips des Typs DS28E17, welche I2C-Befehle via One-Wire empfangen und auf den I<sup>2</sup>C-Bus weitersenden, besitzt der ausgewählte Brückentyp zusätzlich einen Befehlssequenzer. Dieser umfasst 512 Byte und ermöglicht es, Abfolgen von I<sup>2</sup>C-Befehlen im Speicher des Sequenzers zu speichern und später wiederholt auszuführen oder abzurufen. Damit kann beispielsweise für den beschriebenen Anwendungsfall eine Sequenz übertragen und im Sequenzer gespeichert werden, welche das SHT40 Modul konfiguriert und Messwerte ausliest. Um diese Befehlsfolge auszuführen, wird lediglich ein Ausführungsbefehl mit der Speicheradresse und -länge der Sequenz übermittelt. Bei komplexen oder häufig ausgeführten Operationssequenzen minimiert dies das Datenaufkommen auf dem One-Wire-Bus. Aufgrund der vergleichsweise niedrigen Datenrate von 16,3 kbit/s kann dies zu Zeitersparnissen im Programmablauf führen. Auf die konkrete Bedeutung dessen nehmen Abschnitt 2.4 - One-Wire im Überblick und Abschnitt 2.6 - DS28E18 One-Wire-zu-l2C/SPI-Bridge Bezug. [Ana09]

# 2. Grundlagen

### 2.1 Stand der Forschung

In [Mac12] wird die Verwendungsmöglichkeit von One-Wire in der Heim- und Gebäudeautomation untersucht. Dabei wird festgestellt, dass One-Wire aufgrund seiner Eigenschaften wie der Möglichkeit, Sensoren und Aktoren über eine Leitung zu versorgen, eine kostengünstige und zuverlässige Lösung sein kann. Die Verwendung von RJ-45-Steckern und **Twisted-Pair-Kabeln** bietet eine hohe Zuverlässigkeit der Verbindung. Abschlusswiderstände von  $100~\Omega$  werden verwendet, um **Reflexionen** im Leiter zu minimieren. Mit diesem Testaufbau konnte ein **Netzwerkradius** von 360 Meter erreicht werden. Insgesamt bewerten die Autoren One-Wire als vielversprechend für den Einsatz in der Gebäudeautomation.

Die Autoren von [GM15] untersuchen in ihrem Artikel die Einsatzmöglichkeit von One-Wire in einem zuverlässigen Temperaturüberwachungssystem für Satelliten in niedrigen Erdumlaufbahnen. Die Technologie ist dabei besonders interessant, da es sich um "Commercial off-the-shelf" Produkte (sinngemäß: kommerzielle Serienprodukte) handelt, die im Vergleich zu speziell für die Raumfahrt entwickelten Geräten sehr preiswert sind. Als Bus-Master wurde ein **Field Programmable Gate Array (FPGA)** eingesetzt. Verschiedene Topologien und Redundanzsysteme werden auf ihre Fehleranfälligkeit verglichen, um ein robustes System für den Raumfahrteinsatz zu konzipieren.

[Cui10] beschreibt die Verwendung von One-Wire in einem System zur drahtlosen Überwachung von den Klimadaten in Getreidelagern. Dazu wurde eine Messschaltung entworfen, welche aus One-Wire-Temperatursensoren und Analog-Digital-Umsetzern mit daran angeschlossenem Feuchtigkeitssensor besteht. Jede Messschaltung besteht aus einem oder mehrerer dieser Sensoren. Als Master dient ein Mikrocontroller, welcher mittels SPI mit einem Funkmodul verbunden ist, um die Sensordaten drahtlos zu übertragen. Ein Main-Controller empfängt, sammelt und speichert die Daten der drahtlos verbundenen Sensorschaltungen. Das entworfene System ist kosteneffizient, in bestehenden Sensorsystemen leicht nachrüstbar und flexibel. Es verbindet günstige One-Wire-Techno-

logie und analoge Sensorik mit den Vorteilen drahtloser Übertragung.

Die Entwicklung eines Systems zur Überwachung von Hochleistungsrechnern wird in [OD18] beschrieben. Die angestrebten Ziele sind dabei Zuverlässigkeit und simple Prozesse für die Installation und den Betrieb. Um dies zu erreichen wurde ein Mainboard entwickelt, welches über RJ-12 Ports als Sensorschnittstellen sowie einen RJ-45 Port für die Netzwerkverbindung und Stromversorgung mittels Power-over-Ethernet verfügt. Auf dem Mainboard befinden sich außerdem ein Arduino Mikrocontroller, One-Wire-Controller und ein Raspberry-Pi als Add-On über eine Pinleiste. Durch das gewählte Pin-Out der RJ-12 Ports ist es möglich, beliebig I²C oder One-Wire-Sensoren zur Messung verschiedener Parameter anzuschließen. Die Messdaten werden erfasst und an einen zentralen Server übertragen, welcher diese speichert und Auswertungen ermöglicht.

[XXY08] beschreibt ein prototypisches System zur Branderkennung in Gebäuden. Dazu haben die Autoren One-Wire-Temperatursensoren in hexagonalen Anordnungen angebracht, jeweils an den Ecken und im Mittelpunkt der Hexagone. Beim Übertreten von Schwellwerten wechseln die Sensoren in den Alarm-Status, wodurch Brandherde erkannt und durch die gemessenen Temperaturen der alarmierten Sensoren genauer trianguliert werden können. Mittels der gemessenen Temperaturen an umliegenden Sensoren kann außerdem die Ausbreitungsrichtung des Feuers approximiert werden. Ein **FPGA** wird als Controller eingesetzt und aggregiert die Daten. Über eine RS232 Schnittstelle erfolgt die Verbindung mit einem Rechner, auf dem die Daten in einem Programm visualisiert werden können.

Zusammenfassend lässt sich feststellen, dass One-Wire aufgrund der elektrischen Einfachheit und der geringen Kosten verbreitet ist, um kosteneffiziente Sensorsysteme zu entwerfen. Das Thema der Bridge-Treiber von One-Wire zu I<sup>2</sup>C oder ähnlichen Protokollen, womit sich diese Arbeit beschäftigt, sind in der Wissenschaft jedoch noch weitgehend unbeleuchtet.

### 2.2 Linux im Überblick

Der Linux-Kernel bildet die Grundlage für eine Vielzahl von Betriebssystemen wie etwa Ubuntu, Arch Linux oder Fedora. Er bildet die Schnittstelle zwischen Anwendungen und der Hardware des Systems und besitzt uneingeschränkten Zugriff auf die Systemhardware. Dieser privilegierte Namensraum wird als Kernel-Space bezeichnet. Der Kernel-Space verfügt über einen geteilten Speicherbereich, auf

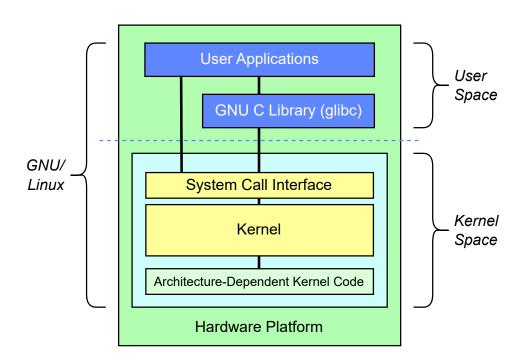

den alle Kernel-Prozesse Zugriff haben. Der Kernel kann in drei übergeordnete Schichten unterteilt werden. Das System Call Interface stellt eine Schnittstelle zur Interaktion mit dem Kernel bereit. Die Vielzahl der Kernel-Funktionen sind unabhängig von der Prozessor-Architektur implementiert. Um die Interaktion mit Hardwarekomponenten aus diesen Funktionen zu ermöglichen, stellt das sogenannte Board Support Package (BSP) architekturspezifischen Code zur Verfügung. Einen allgemeinen Überblick über die Architektur eines Linux-Systems bietet Abbildung 2.1. [Jon07]

Abbildung 2.1: Überblick über die Linux-Systemarchitektur [vgl. Jon07]

Im Gegensatz zum Kernel haben Anwendungen auf dem System keinen direkten Zugriff auf Hardwarekomponenten. Sie werden im sogenannten User-Space ausgeführt. User-Space-Prozesse können dabei über definierte Systemaufrufe (System Calls) mit dem Kernel interagieren und so indirekten Zugriff auf Hardware erlangen und mit dieser interagieren. Jeder Prozess im User-Space besitzt einen eigenen virtuellen Speicherbereich. Die GNU C Bibliothek (glibc) stellt das System Call Interface für Anwendungen bereit sowie Funktionen, um den Ausführungskontext zwischen dem User-Space und dem Kernel-Space zu wechseln (Context-Switching). [Jon07]

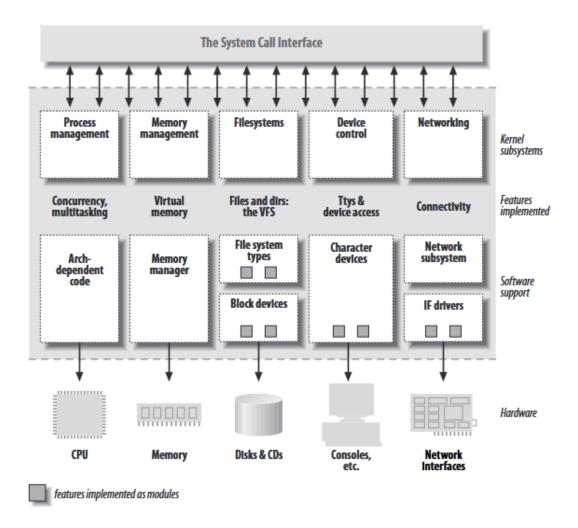

Der Kernel ist in Teilsystemen (Subsystemen) aufgebaut, welche diverse Funktionalitäten bereitstellen, wie in Abbildung 2.2 vereinfacht dargestellt. Beispiele

für Subsysteme sind das Bluetooth-Subsystem, GPIO-Subsystem oder das Real-Time-Clock-Subsystem. Die meisten Subsysteme verfügen über Maintainer, welche für dieses verantwortlich sind. Die Maintainer agieren als Entscheidungsträger und Kontrollinstanz für Änderungen am Code (Patches). Gerätetreiber sind ein zentraler Bestandteil des Kernels und ermöglichen die Nutzung der Geräte unter Linux. Sie implementieren gerätespezifisch standardisierte Schnittstellen, um Zugriffe über das System Call Interface zu ermöglichen. [Jon07]

Abbildung 2.2: Überblick über die Linux-Kernel-Struktur [CRK05, Figure 1-1]

### 2.3 Terminologie

Im Folgenden wird auf die Bussysteme One-Wire und I<sup>2</sup>C eingegangen. Bei beiden Bussen handelt es sich um sogenannte Master-Slave-Busse, bei denen ein Gerät (Master) die Steuerung der Schreibzugriffe anderer Geräte (Slaves) auf dem Bus steuert. Da sich die Begrifflichkeiten aus der Sklaverei ableiten, wird

auf die Verwendung dieser Begrifflichkeiten heute häufig verzichtet. Auch der Linux Code of Conduct empfiehlt die Verwendung anderer Begrifflichkeiten, wie Main und Target.

Im Rahmen dieser Arbeit werden die Begriffe **Master/Slave** dennoch bewusst und ausschließlich im Kontext von One-Wire verwendet. Hintergrund ist, dass offizielle Dokumente und die Implementierung in Linux weiterhin diese Begriffe verwenden.

Für I<sup>2</sup>C hingegen werden ausschließlich die Begriffe **Controller/Target** verwendet. Dies entspricht der Spezifikation von I<sup>2</sup>C seit Version 7, sowie dem Code of Conduct des Linux-Kernels.

### 2.4 One-Wire im Überblick

One-Wire ist ein serieller Feldbus, welcher durch die Firma Dallas Semiconductor <sup>1</sup> entwickelt wurde. Dabei wird für die Datenübertragung und Stromversorgung nur ein gemeinsamer Leiter benötigt, woher sich auch der Begriff "One-Wire" (auch "OneWire" oder "1-Wire") ableitet. Um dies zu ermöglichen verfügen One-Wire-Geräte über einen Kondensator, welcher sich über die Datenleitung mit Strom versorgt. Diese verfügt über eine Nominalspannung ( $V_{PUP}$ ) und wird zur Kommunikation für definierte Zeitintervalle auf ein niedrigeres Potenzial unterhalb eines Schwellwertes  $(V_{TL})$  gesenkt (1-Bit: max. 15 µs, 0-Bit: min. 60 µs). Diese Art der Spannungsversorgung wird als parasitäre Stromversorgung bezeichnet. Einige One-Wire-Geräte können jedoch auch extern mit ihrer Nominalspannung versorgt werden. Im Falle eines Spannungsverlustes fallen alle One-Wire-Geräte in einen definierten Reset-Zustand zurück. Für einige wenige Slaves, wie den DS28E182, kann das zur Folge haben, dass diese neu initialisiert oder konfiguriert werden müssen, wenn zum Beispiel die Spannungsversorgung unterbrochen wurde. Alle One-Wire-Geräte lassen sich entweder als Master-Geräte (Master) oder Slave-Geräte (Slave) einordnen. Master übernehmen die Steuerung der Kommunikation und bilden die Schnittstelle zu dem übergeordneten System, wie etwa einem Steuerungsgerät oder Rechner (siehe Unterabschnitt 2.4.1 - Aufbau eines One-Wire-Netzes). Slaves kommunizieren ausschließlich mit dem Master und besitzen Funktionen entsprechend ihrer Pro-

<sup>&</sup>lt;sup>1</sup>Dallas Semiconductor wurde 2001 von Maxim Integrated gekauft. 2021 übernahm Analog Devices beide Unternehmen und ist heutiger Lizenzhaber von One-Wire. [Wik22]

<sup>&</sup>lt;sup>2</sup>Alle One-Wire-Geräte beginnen mit dem Kürzel "DS" für *Dallas Semiconductor*. Diese Benennung wurde von den späteren Lizenzhabern übernommen und besteht weiterhin.

duktkategorie. Die Übertragungsrate von One-Wire beträgt im Standardfall 16,3 kbit/s. Der sogenannte "Overdrive"-Modus kann optional bei einigen Slaves aktiviert werden, um die Übertragungsrate auf etwa das Achtfache (bis zu 114,2 kbit/s) zu erhöhen. Gleichzeitig können weniger Slaves im Overdrive-Modus als im Standardübertragungsmodus gesteuert werden, wenn die Slaves parasitär betrieben werden. Grund hierfür ist, dass durch die kürzeren Zeitintervalle von Overdrive und den Spannungsabfall durch die Slaves ab einer gewissen Anzahl Slaves die Kondensatoren nicht mehr vollständig in einem Zeitslot aufgeladen werden können. Im Falle des DS2480B Masters ist es möglich etwa 30 Slaves regulär, und etwa neun Slaves im Overdrive-Modus zu betreiben. [Ana08; Ana09; Ana11a; Dem13]

Alle One-Wire-Geräte verfügen über eine 64-Bit Identifikationsnummer, der sogenannten *ROM-ID*, zur eindeutigen Identifikation. Beginnend beim **Least Significant Bit (LSb)** der *ROM-ID* steht dabei der Family-Code, eine 8-Bit Nummer, welche den Typ des Gerätes identifiziert. Die folgenden 48 Bits sind eine eindeutige Seriennummer des Geräts. Die höchstwertigen acht Bit sind eine Prüfziffer. Auf die Berechnung dieser Prüfziffern wird in Unterabschnitt 2.4.3 - Zyklische Redundanzprüfung (CRC) näher eingegangen. [Ana24]

Da es sich um ein Master-Slave-Protokoll handelt, wird jegliche Kommunikation durch den Master des Busses initiiert und gesteuert. Außerdem stellt dieser die Schnittstelle zum übergeordneten System dar, etwa einer SPS Steuerung oder einem Rechner. Unter Linux wird diese Schnittstelle durch das sogenannte W1-Subsystem des Kernels bereitgestellt (siehe Abschnitt 3.1 - W1-Subsystem: Das Kernel One-Wire-Subsystem). Zu jeder Zeit kann sich nur ein Master im Netz befinden. Die Kommunikation im One-Wire-Netzwerk ist halb-duplex, die Übertragung ist also bidirektional, aber auf ein Gerät gleichzeitig beschränkt. Der Master agiert dabei steuernd. Er initiiert jede Kommunikation und fordert Antworten von Slaves aktiv an.

#### 2.4.1 Aufbau eines One-Wire-Netzes

Über zwei Drähte, die Datenleitung und eine Masse-Leitung, werden die Slaves mit dem Master verbunden. Die Topologie von One-Wire-Netzen kann frei gewählt werden, hat jedoch Einfluss auf die maximale physische Größe des Netzwerks. Die Gesamtlänge der Kabel im Netzwerk wird **Netzwerkgewicht** genannt, die Entfernung vom Master zum am weitesten entfernten Slave heißt **Netzwerkradius**. Die meisten Implementierungen lassen sich als Reihen-, Bus- oder Stern-

topologie kategorisieren, oder als eine Kombination derer. Bei Netzwerken mit Bustopologie ist jedoch zu beachten, dass es vermehrt zu **Reflexionen** kommen kann, welche die Datenübertragung stören und zu Datenfehlern führen können. Da One-Wire zwar über Prüfsummen, jedoch keine Möglichkeit der Fehlerkorrektur verfügt, bedeuten fehlerhafte Übertragungen eine erneute Ausführung und somit potenziell höhere Datenaufkommen auf dem Bus, bei gleichbleibenden Anfragen. Das **Netzwerkgewicht** eines One-Wire-Netzes kann bis zu etwa 200 Meter betragen. Die Verwendung elektrotechnischer Maßnahmen kann dies auf bis über 500 Meter erhöhen. [Ana01b]

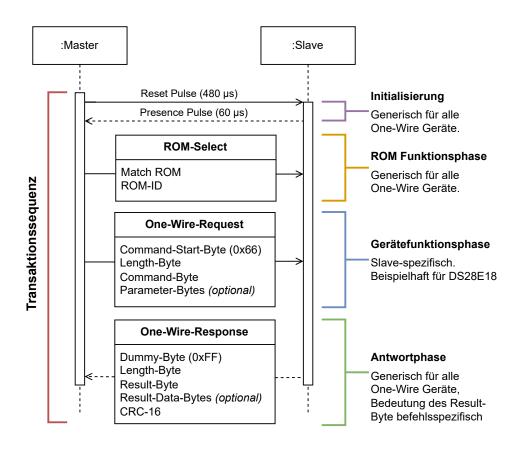

Abbildung 2.3: Beispielhafte One-Wire-Kommunikationssequenz

#### 2.4.2 Ablauf der One-Wire-Kommunikation

Die Kommunikation unter One-Wire kann in drei Phasen eingeteilt werden. In der ersten Phase wird der Bus initialisiert (Bus-Reset / Initialization). Dazu sendet der Master einen Reset-Puls, der mit 480  $\mu$ s länger als die Pegel für Bits sind. Alle mit dem Bus verbundenen Slaves antworten dem Master darauf mit ei-

nem Presence Pulse (min. 60 µs), der die Anwesenheit mindestens eines Slaves auf dem Bus signalisiert. Es folgt die zweite Phase, die "ROM-Funktionsphase" (englisch ROM function phase). Darin werden Funktionen zur Identifizierung der Slaves auf dem Bus, sowie zur Adressierung und Selektion von Slaves mittels ROM-ID ausgeführt. Die dritte Phase ist die "Gerätefunktionsphase" (englisch device function phase), in der gerätespezifische Funktionen ausgeführt werden können (Request). In der Antwortphase (One-Wire-Response) sendet der Slave einen Status und gegebenenfalls Daten-Bytes als Antwort auf die Request. Alle Phasen bilden zusammen die Transaktionssequenz. Eine vollständige Transaktionssequenz mit ihren Phasen ist in Abbildung 2.3 abgebildet. [Ana24; Dem13]

#### **ROM-Funktionsphase**

In der ROM-Funktionsphase gibt es zwei Arten von Befehlen. Die Befehle Read ROM und Search ROM bilden eine vollständige One-Wire-Kommunikation. Das bedeutet, die Slaves senden ihre Antwort auf den Befehl, woraufhin die Kommunikation beendet ist. Es folgt keine Gerätefunktionsphase.

(Overdrive) Skip ROM, (Overdrive) Match ROM und Resume Command sind selektierende Aktionen und die Grundlage für nachfolgende Befehle der Gerätefunktionsphase. Sie stehen nie allein sondern werden immer von einer Gerätefunktionsphase gefolgt. Eine vollständige Liste aller verfügbarer ROM-Funktionsbefehle befindet sich in Tabelle 2.1.

Tabelle 2.1: Übersicht über One-Wire ROM-Funktionsbefehle [vgl. Ana24, S. 18 f.]

| ROM Funktion        | Byte | Beschreibung                                                |

|---------------------|------|-------------------------------------------------------------|

| Read ROM            | 0x33 | Auslesen der ROM-ID (nur auf Single-<br>Slave-Bus)          |

| Search ROM          | 0xF0 | ROM-ID Suche                                                |

| Skip ROM            | 0xCC | Adressierung aller Slaves                                   |

| Match ROM           | 0x55 | Adressierung eines Slaves mittels ROM-ID                    |

| Resume Command      | 0xA5 | Zuletzt adressierten Slave erneut adressieren               |

| Overdrive Skip ROM  | 0x3C | Adressierung aller Slaves im Overdrive-<br>Modus            |

| Overdrive Match ROM | 0x69 | Adressierung eines Slaves mittels ROM-ID im Overdrive-Modus |

Read ROM und Search ROM sind die einzigen Befehle, welche keine Gerätefunktionsphase im Anschluss zulassen. Read ROM wird genutzt, um die **ROM-ID** des

Slaves auszulesen, wenn sich nur ein einziger Slave auf dem Bus befindet. Bei mehreren Slaves auf dem Bus oder, wenn die Anzahl Slaves unbekannt ist, kann mit Search ROM die **ROM-ID** Suche auf dem Bus begonnen werden. Eine Beschreibung des Suchalgorithmus findet sich in [Ana03].

Alle weiteren Befehle werden genutzt, um einen oder mehrere Slaves für die darauffolgende Gerätefunktion zu adressieren. Der Befehl Skip ROM adressiert alle Slaves auf dem Bus und ist damit ähnlich eines Broadcasts zu verstehen. Der Befehl Match ROM wird genutzt um einen Slave zu selektieren, indem dessen ROM-ID als Parameter übermittelt wird. Resume Command ist eine Wiederholung der letzten Selektion, beispielsweise wenn mehrere Befehle direkt aufeinander folgend an den gleichen Slave gesendet werden. Die Befehle Overdrive Skip ROM und Overdrive Match ROM sind äquivalent zu Skip ROM und Match ROM, versetzen aber gleichzeitig den Bus in den "Overdrive-Modus". [Ana24]

#### Gerätefunktionsphase

Nach erfolgreicher ROM-Funktionsphase beginnt die Gerätefunktionsphase. In dieser können gerätespezifische Funktionen ausgeführt werden, wie beispielsweise das Schreiben von Daten an einer Speicheradresse des Slaves oder Lesen eines Sensorwertes. Der konkrete Aufbau dieser Nachrichten und damit des Pakets variieren stark zwischen verschiedenen One-Wire-Slaves und sind dem entsprechenden Datenblatt zu entnehmen. Grundlegend bestehen Sie jedoch aus einem Befehls-Byte und darauffolgenden Parameter-Bytes. Das Ende der Übertragung wird durch ein Release-Byte signalisiert, dessen Wert ebenfalls geräteabhängig ist.

Nachfolgende Ausführungen beziehen sich konkret auf den DS28E18.

Jeder Geräte-Befehl des DS28E18 beginnt zunächst mit dem Befehlsstart-Byte (Command-Start-Byte, 0x66) gefolgt vom Längen-Byte (Length-Byte), welches die Gesamtlänge der darauf folgenden Befehls- und Parameter-Bytes angibt. Die minimale Länge ist dabei 1, im Falle eines parameterlosen Gerätebefehls. Es folgt das Befehls-Byte (Command-Byte) und im Anschluss optional die Parameter-Bytes. Das Release-Byte 0xAA schließt die Übertragung ab. [Ana24]

#### **Antwortphase (One-Wire-Response)**

In der Antwortphase sendet der Slave eine (One-Wire-)Response zurück an den Master. Jede Response besteht dabei aus mindestens fünf Bytes.

Tabelle 2.2: Bytes einer One-Wire-Befehlssequenz des DS28E18 [Ana24]

| Byte-<br>Offset | Länge<br>in By-<br>tes | Bedeutung          | Beschreibung                                                            |

|-----------------|------------------------|--------------------|-------------------------------------------------------------------------|

| 0x00            | 1                      | Command-Start-Byte | Signalisiert Beginn einer Be-<br>fehlssequenz                           |

| 0x01            | 1                      | Length-Byte        | Länge der folgenden Bytese-<br>quenz                                    |

| 0x02            | 1                      | Command-Byte       | Auszuführender Gerätebefehl                                             |

| 0x03            | n                      | Parameter-Bytes    | Parameter zum Com-<br>mand-Byte (optional, Länge<br>n = LengthByte - 3) |

Das erste Byte der Antwort ist immer ein Dummy-Byte mit dem Wert 0xFF. Dieses dient lediglich zur Synchronisation des Takts, wird verworfen und auch in der CRC Berechnung nicht einbezogen. Es folgt ein Length-Byte, welches die Anzahl folgender Bytes angibt. Dieses ist mindestens 1, da mindestens das Ergebnis-Byte gesetzt ist. Dieses folgt direkt auf das Length-Byte. Ein Wert von 0xAA steht für eine erfolgreiche Befehlsausführung, andere Werte sind Abhängig vom Chiptyp und Befehl und im jeweiligen Datenblatt definiert. Ist das Length-Byte größer als eins, folgen LengthByte – 1 Antwort-Bytes (Result-Data-Bytes). Das Format und die Interpretierung der Daten ist dabei ebenfalls im Datenblatt des Chips definiert. Zwei Bytes für die CRC-16 Prüfsumme stehen am Ender der Response. Berechnet werden diese über alle vorherigen Bytes der Sequenz, abzüglich des Dummy-Byte. [Ana24]

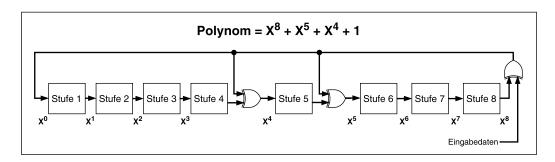

### 2.4.3 Zyklische Redundanzprüfung (CRC)

Die Zyklische Redundanzprüfung, kurz CRC, ist eine Methode zur Erkennung von Übertragungsfehlern. Sie basiert auf dem Prinzip der Polynomdivision, indem das Restpolynom mittels wiederholter bitweiser XOR-Operation berechnet wird. Die zu übertragenden Bits werden dabei als Faktoren eines Polynoms betrachtet. Um die CRC zu berechnen, wird zunächst ein Generatorpolynom der Länge n bestimmt. Dieses entspricht gleichzeitig der maximalen Länge der CRC-Prüfsumme, den man als CRC-n bezeichnet. Im Falle eines 8-Bit CRC also etwa CRC-8, für 16-Bit CRC CRC-16, et cetera. Die Eingabe-Bitfolge wird nun um (n-1) Bits mit dem Wert 0 zum sogenannten Rahmen verlängert. Rahmen und Generatorpolynom werden vom **Most Significant Bit (MSb)** aus am ersten Bit dem Wert 1 aneinander ausgerichtet und die Bits von Rahmen und Generatorpo-

lynom mittels XOR dividiert. Dieser letzte Schritt wird nun so lange wiederholt, bis das Restpolynom weniger **relevante Stellen** als das Generatorpolynom hat. Das Ergebnis ist die CRC-Prüfsumme. [Ana01a, S. 3 f.; Wik24; Gee16]

Die Wahl eines spezifischen Polynoms beeinflusst die CRC Berechnung direkt und muss den Kommunikationspartnern bekannt sein. Im Falle des One-Wire CRC-8, wie es bei der One-Wire **ROM-ID** zum Einsatz kommt, handelt es sich dabei um das Polynom  $X^8 + X^5 + X^4 + 1$ . Neben CRC-8 findet unter One-Wire auch CRC-16 als Prüfsumme für One-Wire-Pakete Anwendung. Das Polynom hierfür lautet  $X^{16} + X^{15} + X^2 + 1$ . Da es sich bei der Berechnung CRC um XOR-Operationen handelt, kann diese mit Hilfe eines Schieberegisters auch in Hardware implementiert werden. Dies ist in One-Wire-Geräten der Fall. [Ana01a, S. 3 f., 9–11]

Abbildung 2.4: One-Wire CRC-8 Schieberegister [vgl. Ana01a, Figure 2]

Um eine empfangene Bitfolge zu prüfen, wird derselbe Prozess auf die empfangene Bitfolge einschließlich der empfangenen CRC-Prüfsumme angewendet. Da die CRC eine Berechnung des Restpolynoms ist und dieser Rest nun am Ende der Bitfolge ergänzt wurde, ist das Ergebnis bei einer fehlerfreien Übertragung 0. [Ana01a, S. 4]

### 2.5 I<sup>2</sup>C im Überblick

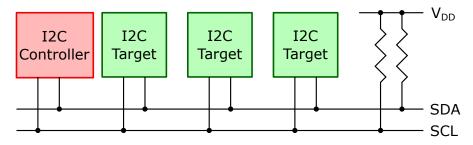

Der I<sup>2</sup>C-Bus (Inter Integrated Circuit Bus) ist eine serielle Schnittstelle entwickelt von Philips Semiconductors (heute NXP Semiconductors). Sie kommt mit insgesamt drei Leitungen aus: SDA (Serial Data Line) für Daten, SCL (Serial Clock Line) für den Takt und eine Masseverbindung. I<sup>2</sup>C wird häufig zur internen Kommunikation von Komponenten auf Platinen oder innerhalb von Geräten verwendet und wurde zu diesem Zweck entwickelt. [kdcom24; Dem13]

Jeder I<sup>2</sup>C-Bus verfügt über exakt einen Controller, an dem mehrere Targets angeschlossen werden können. Dies erfolgt in der Regel in Form von Leiterbahnen

Abbildung 2.5: Aufbau eines einfachen I<sup>2</sup>C-Bus [kdcom24]

auf einer Platine. Der Aufbau eines einfachen I<sup>2</sup>C-Bus ist in Abbildung 2.5 dargestellt. I<sup>2</sup>C-Targets besitzen fest zugewiesene 7 Bit Adressen, über welche diese durch den Controller adressiert werden können. Die Kommunikation wird dabei durch den Controller gesteuert und initiiert.

Tabelle 2.3: I<sup>2</sup>C Übertragungsraten [vgl. Dem13, Tabelle 8.1]

| Modus           | Datenrate  | Direktionalität |

|-----------------|------------|-----------------|

|                 |            |                 |

| Standard Mode   | 100 kbit/s | bidirektional   |

| Fast Mode       | 400 kbit/s | bidirektional   |

| Fast Mode Plus  | 1 Mbit/s   | bidirektional   |

| High Speed Mode | 3,4 Mbit/s | bidirektional   |

| Ultra Fast Mode | 5 Mbit/s   | unidirektional  |

Unterstützt werden verschiedene Taktraten zwischen 100 kbit/s und 5 Mbit/s. Alle Betriebsarten außer der "Ultra Fast Mode" sind abwärtskompatibel. Besagter Modus stellt außerdem eine Besonderheit dar, da der "Ultra Fast Mode" nur unidirektionale Kommunikation auf dem Bus erlaubt. Daher wird dieser ausschließlich eingesetzt, wenn Targets nur Befehle empfangen aber keine Daten senden dürfen. Im Gegensatz zu One-Wire erlaubt I²C die Verwendung mehrerer Controller auf dem selben Bus. Durch Vergleich der gesendeten Daten mit der SDA-Leitung erkennt der Controller, wenn ein anderer Controller ein dominantes Signal (Null-Bit) sendet und wechselt in den Target-Modus, bis der Bus wieder frei ist. Damit wird eine Bus-Arbitrierung erreicht. [Dem13]

Weitere Details zur Implementierung von I<sup>2</sup>C und der Interaktion mit Controllern und Targets sind in Abschnitt 3.2 - I2C-Subsystem beschrieben.

### 2.6 DS28E18 One-Wire-zu-I<sup>2</sup>C/SPI-Bridge

Der DS28E18 ist eine Kommunikationsbrücke, welche einen dahinter liegenden I<sup>2</sup>C- oder SPI-Bus über eine One-Wire-Schnittstelle verfügbar macht (siehe Ab-

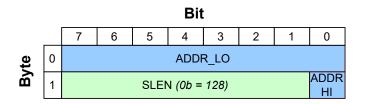

bildung 2.6). Damit kann eine effektive Reichweite von etwa 100 Meter erreicht werden und die notwendige Verdrahtung wird reduziert. Im Vergleich zum in der Funktion ähnlichen DS28E17 verfügt der DS28E18 über einen Befehlssequenzer von 512 Byte Größe. Dieser kann mit mehreren Sequenzen von I²C oder SPI-Befehlen programmiert werden. Dazu werden in einem One-Wire-Paket mit dem Befehl Write Sequencer bis zu 128 Byte I²C/SPI-Befehle an eine als Parameter übermittelte Speicheradresse im **Static random-access memory (SRAM)** geschrieben. Über einen One-Wire-Befehl können diese beliebig oft ausgeführt werden. Dazu dient der Befehl Run Sequencer mit Parametern für die Speicheradresse und die Anzahl auszuführender Bytes (Länge). Mittels Read Sequencer können anschließend Ergebnisse zurückgelesen werden. Dieser liest bis zu 128 Byte aus dem Sequenzer-**SRAM**. [Ana24]

Abbildung 2.6: Grundlegende Funktion des DS28E18 als I2C-Bridge

Das Gerät unterstützt außerdem mehrere Übertragungsraten. Für I²C und SPI sind das 100 kHz, 400 kHz oder 1 MHz. SPI kann außerdem mit 2,3 MHz betrieben werden. Die Konfiguration erfolgt ebenfalls über One-Wire mittels des Befehls Write Configuration. Die Parameter werden dabei in einer Bitmaske kodiert. Dazu gehören der SPI-Modus, das Protokoll (SPI/I²C), das Verhalten bei NACK Paketen und die Geschwindigkeit. Als I²C-Controller stehen außerdem zwei GPIO-Pins am Chip zur Verfügung, welche mittels des Gerätebefehls Write GPIO Configuration konfiguriert und Read GPIO Configuration gelesen werden können. [Ana24]

#### 2.6.1 Kommunikation mit dem DS28E18

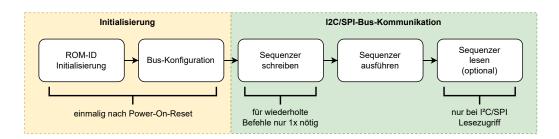

Der DS28E18 stellt einen I<sup>2</sup>C-Bus bereit. Bevor dieser genutzt werden kann, muss der Chip jedoch initialisiert werden.

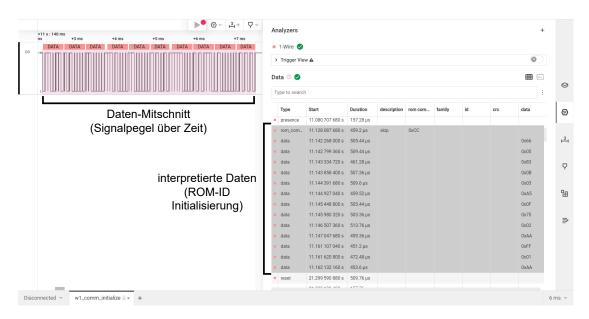

Bei einem **Power-On-Reset (POR)** wird die Gerätekonfiguration zurückgesetzt. Dazu zählt auch die **ROM-ID**, welche im Falle des DS28E18 initial erst aus einem ROM-Speicher gelesen und so initialisiert (aktiviert) werden muss. Im Anschluss kann der I<sup>2</sup>C-Bus konfiguriert werden. Beide Aktionen sind jedoch nur nach einem **POR** einmalig nötig. Um nun auf dem I<sup>2</sup>C-Bus zu kommunizieren, muss der Sequenzer zunächst beschrieben werden. Die im Sequenzer programmierten Befehle können dann ausgeführt werden. Um Daten auszulesen, beispielsweise Messwerte, kann der Sequenzer dann gelesen werden.

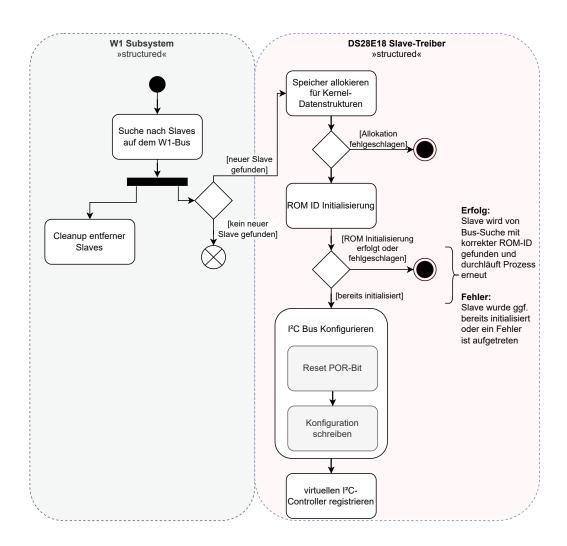

Die genannten Funktionen werden im Weiteren näher erläutert, eine Übersicht des Ablaufs findet sich in Abbildung 2.7.

Abbildung 2.7: DS28E18 Schrittfolge zur Ausführung eines I<sup>2</sup>C/SPI-Befehls

Jeder One-Wire-Befehl an den DS28E18 beginnt mit dem Byte 0x66, welches den Beginn einer Befehlssequenz signalisiert, gefolgt von einem Length-Byte sowie einem Gerätebefehl und dessen Parameter (siehe Gerätefunktionsphase). Eine Übersicht aller Gerätebefehle und deren Parameter ist in Abbildung 2.8 dargestellt. [Ana24]

#### ROM-ID Initialisierung

Abbildung 2.8: DS28E18 One-Wire-Befehlsstruktur [Ana24, Figure 1]

#### I<sup>2</sup>C/SPI-Bus Konfiguration

Der DS28E18 kann wahlweise als I<sup>2</sup>C- oder SPI-Controller eingesetzt werden. Um das gewählte Protokoll sowie weitere Bus-Attribute zu konfigurieren, stellt das Gerät den Befehl WriteConfiguration bereit. Der DS28E18 verfügt über Power-On-Defaults, welche nach der **ROM-ID**-Initialisierung überschrieben werden können. Die Standardkonfiguration ist nachfolgend in Tabelle 2.4 beschrieben.

Tabelle 2.4: DS28E18 Standard Buskonfiguration [Ana24]

| Attribut        | Wert                                        |  |  |

|-----------------|---------------------------------------------|--|--|

|                 | (, , , , , , , , , , , , , , , , , , ,      |  |  |

| SPI-Modus       | Mode 0 (kein Einfluss bei I <sup>2</sup> C) |  |  |

| Protokoll       | I <sup>2</sup> C                            |  |  |

| Ignoriere NACK  | Ausführung abbrechen                        |  |  |

| Geschwindigkeit | 400 kHz                                     |  |  |

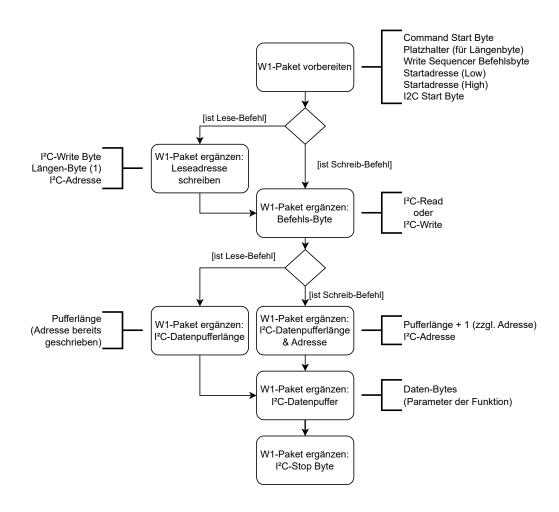

#### Ausführen von Befehlen auf dem Bus

Der DS28E18 verfügt über einen Befehlssequenzer, in welchem die I²C-Befehle gespeichert werden, bevor diese auf dem Bus gesendet werden. Dabei ist jede einzelne dieser Aktionen — das Schreiben des Sequenzers, das Senden der Sequenz, (gegebenenfalls) das Lesen der Daten — ein eigener One-Wire-Befehl, der übermittelt werden muss. Dabei ist zu beachten, dass über I²C gelesene Daten in den Sequenzer-Speicher des DS28E18 geschrieben werden. Daher müssen für Lesezugriff direkt nach dem Lesebefehl Dummy-Bytes in der Länge der zu lesenden Daten geschrieben werden. Diese werden mit den gelesenen Werten vom Bus überschrieben und können anschließend aus dem Sequenzer gelesen werden. Der Ablauf zum Lesen eines Wertes über den I²C-Bus kann in Abbildung 2.7 nachvollzogen werden.

Die Nutzung eines Sequenzers erlaubt es, Befehle und Befehlssequenzen zwischenzuspeichern. Diese können jederzeit erneut aufgerufen und damit auf den Bus übermittelt werden. Bei effizienter Nutzung des **SRAM**-Speichers ist es so möglich, Befehle nur einmal zu programmieren und anschließend mit minimaler One-Wire-Buslast Befehlssequenzen wiederholt auszuführen, da hierfür nur Startadresse und Länge der Sequenz übertragen werden müssen. Insbesondere für sich häufig wiederholende oder lange Befehlsfolgen kann dies, aufgrund der geringen Übertragungsrate von One-Wire im Vergleich zu I<sup>2</sup>C und SPI, zu messbar geringeren Ausführungszeiten führen.

## 3. One-Wire und I<sup>2</sup>C unter Linux

### 3.1 W1-Subsystem: Das Kernel One-Wire-Subsystem

Der Linux-Kernel ist in sogenannte Subsysteme unterteilt. Dabei folgt der Begriff als solches keiner genauen Definition, sondern beschreibt vielmehr eine Teilkomponente der Architektur von Linux, welche von eigenen Maintainern weitgehend autark verwaltet wird. Subsysteme können die Implementierung eines Frameworks, eines Protokolls oder komplexer Teilsysteme wie den Netzwerk-Stack umfassen. Subsysteme sind maßgebend für die Architektur von Linux.

Das W1-Subsystem, oder auch <code>One-Wire-Subsystem</code>, bildet ein Framework für die Unterstützung von One-Wire unter Linux und ist im Kernel-Sourcetree unter linux/drivers/w1 angesiedelt. Das grundlegende Protokoll und Schnittstellen werden in  $w1\_io.c$  implementiert, etwa das Lesen und Schreiben von Bits, Bytes und Byte-Blöcken.

Das W1-Subsystem unterscheidet grundsätzlich zunächst zwischen zwei Arten von Geräten: Master und Slave (siehe Abschnitt 2.4 - One-Wire im Überblick). Treiber für Slaves sind dabei als sogenannte Family Driver für einzelne **One-Wire-Gerätefamilien** implementiert. [kdcom23a]

One-Wire-Master Treiber implementieren neben einem definierten Interface jeweils die Funktionen des konkreten Geräts. Dieses definiere Interface stell Funktionen zum Schreiben und Lesen von Bits (touch\_bit) sowie das Zurücksetzen des Busses (reset\_bus) bereit. Diese Funktionen müssen von jedem Master-Treiber implementiert werden. Das Subsystem bietet auch Treiber für emulierte Master, etwa durch Bit-Banging über GPIO Pins. Emulierte Master-Treiber müssen dabei nur das Lesen (read\_bit) und Schreiben (write\_bit) von Bits implementieren. Im sysfs werden die Funktionen des One-Wire-Masters zur Interaktion aus dem User-Space in Dateien bereitgestellt. Die Schnittstelle ist in Abbildung 3.1 abgebildet.

Slave Treiber im Gegensatz dazu registrieren eine **One-Wire-Gerätefamilie** beim W1-Subsystem und populieren ein struct w1\_family\_ops, in dem Gerätefunk-

| <xx-xxxxxxxxxxx></xx-xxxxxxxxxxx> | A directory for a found device. The format is family-serial    |

|-----------------------------------|----------------------------------------------------------------|

| bus                               | (standard) symlink to the w1 bus                               |

| driver                            | (standard) symlink to the w1 driver                            |

| w1_master_add                     | (rw) manually register a slave device                          |

| w1_master_attempts                | (ro) the number of times a search was attempted                |

| wl_master_max_slave_count         | (rw) maximum number of slaves to search for at a time          |

| w1_master_name                    | (ro) the name of the device (w1_bus_masterX)                   |

| w1_master_pullup                  | (rw) 5V strong pullup 0 enabled, 1 disabled                    |

| w1_master_remove                  | (rw) manually remove a slave device                            |

| w1_master_search                  | (rw) the number of searches left to do, -1=continual (default) |

| w1_master_slave_count             | (ro) the number of slaves found                                |

| w1_master_slaves                  | (ro) the names of the slaves, one per line                     |

| w1_master_timeout                 | (ro) the delay in seconds between searches                     |

| w1_master_timeout_us              | (ro) the delay in microseconds between searches                |

|                                   |                                                                |

Abbildung 3.1: One-Wire-Master sysfs Interface [kdcom23a]

tionalitäten definiert werden. Wird ein Slave an einen Master angeschlossen, für dessen Familie kein Treiber im Subsystem registriert ist, stellt das Subsystem eine Schnittstelle zur Kommunikation mittels binärem Datenaustausch bereit. Im **sysfs**-Verzeichnis des Slaves wird eine rw-Datei erzeugt, welche ein bidirektionaler Stream zum One-Wire-Bus ist. Über diese Datei können Daten sowohl geschrieben als auch gelesen werden. [kdcom23a]

Weiterhin ist ein Zugriff via Netlink möglich. Netlink ist ein weiteres Kernel-Subsystem, welches die Interaktion mit Kernelmodulen aus dem User-Space mittels Sockets vom Typ AF\_NETLINK bereitstellen kann. Eine One-Wire-Schnittstelle dafür ist in linux/drivers/w1/w1\_netlink.c implementiert und stellt alle bisher beschriebenen Funktionalitäten von One-Wire und dem One-Wire-Subsystem bereit. Auf diesen Anwendungsfall wird im Rahmen dieser Arbeit nicht weiter eingegangen. [kdcom23b]

#### One-Wire Slave-Treiber

Um Treiber für eine Familie von One-Wire-Geräten zu implementieren, stellt der Linux-Kernel unter include/linux/w1.h verschiedene Strukturen und Makros bereit. Die wichtigsten sind dabei die Strukturen struct w1\_family\_ops, sowie das Makro module\_w1\_family.

Die Struktur struct w1\_family beinhaltet grundlegende Informationen zur One-

```

struct w1_family {

1

struct list_head family_entry;

2

u8 fid;

3

const struct w1_family_ops *fops;

4

const struct of_device_id *of_match_table;

atomic_t refcnt;

};

7

8

struct w1_family_ops {

9

int (*add_slave)(struct w1_slave *sl);

10

void (*remove_slave)(struct w1_slave *sl);

11

const struct attribute_group **groups;

const struct hwmon_chip_info *chip_info;

13

};

14

```

Quellcode 3.1: One-Wire Basis-Kernelstrukturen [kdcom20]

Wire-Gerätefamilie. Das Feld fid definiert dabei den Family Code. Wird ein neuer Slave auf dem Bus erkannt, wird der über dieses Feld zugeordnete Treiber vom Subsystem geladen. Wenn kein Treiber für die Familie registriert ist, greift die generische Fallback-Implementierung (Fallback-Slave-Treiber). Im Feld fops wird eine Struktur der verfügbaren Operationen für die Familie hinterlegt. Konkret sind das die Implementierungen der Funktionen add\_slave und remove\_slave, welche aufgerufen werden, wenn ein Slave neu erkannt oder vom Bus entfernt wurde. Diese können beispielsweise genutzt werden, um Initialisierungen durchzuführen, Datenstrukturen anzulegen oder Speicher beim Entfernen wieder freizugeben. Das Makro module\_w1\_family reduziert nötigen Boilerplate-Code durch die Definition der Kernelmodulfunktionen module\_init und module\_exit. Außerdem registriert das Makro den Treiber im W1-Subsystem durch Aufruf der Funktion w1\_register\_family. [kdcom20]

### 3.2 I2C-Subsystem

Auch I<sup>2</sup>C ist im Linux-Kernel als eigenes Subsystem implementiert. Dies ist das I2C-Subsystem. Das Subsystem stellt neben der Implementierung von I<sup>2</sup>C auch SMBus, ein Subset von I<sup>2</sup>C, bereit. Das I2C-Subsystem verwendet dabei in Code und Dokumentation zum Teil abweichende Schreibweisen von der Spezifikation, zum Beispiel "I2C" anstelle von "I<sup>2</sup>C". Weiterhin wird die Bezeichnung "Adapter" für Controller, sowie "Client" für Targets verwendet. [kdcom24]

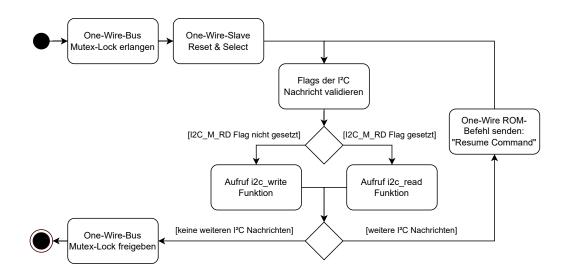

Das I2C-Subsystem unterstützt die manuelle Registrierung von I²C-Controllern durch Aufruf der Kernelfunktion i2c\_add\_adapter. Jeder I²C-Bus erhält vom Subsystem eine Nummer und bildet damit einen logischen I²C-Bus mit einem logischen I²C-Controller. Ein logischer Controller kann entweder einem physischen Controller zugeordnet sein, oder mittels weiteren Abstraktionen in Software einem anderen Gerät. Solche Anwendungsfälle umfassen beispielsweise I²C-Multiplexing, bei dem ein Controller mehrere logische Busse steuert, oder Implementierungen mittels **Bit-Banging**. Im Falle des DS28E18 findet eine Indirektion über One-Wire mit entsprechender Logik statt. [kdcom22]

#### Interaktion mit dem I2C-Subsystem

Das I2C-Subsystem stellt, ähnlich wie das W1-Subsystem ein **sysfs** Interface bereit. Über dieses kann mit Targets auf dem Bus interagiert werden. Üblicherweise ist das Interface unter /sys/bus/i2c zu finden. [kdcom22]

Eine Abstraktion zur vereinfachten Interaktion mit dem I<sup>2</sup>C-Bus bietet die Programmsuite i2c-tools. Diese stellt diverse User-Space-Tools bereit, welche I<sup>2</sup>C-Funktionalitäten implementieren und abstrahieren. Damit können Werte gelesen (i2cget) oder geschrieben (i2cset) werden, oder kombinierte Schreib- und Lesezugriffe (i2ctransfer) getätigt werden. Außerdem können Geräte und Busse erkannt (i2cdetect) werden. Diese Programme werden auch im Rahmen dieser Arbeit genutzt, um mit Targets zu interagieren.

# 4. Konzeption

### 4.1 Beschreibung Anwendungsfall / Versuchsaufbau

Das Steuergerät verfügt über einen One-Wire-Master von Typ DS2482S. Dieser Master ist über I²C mit dem Steuergerät verbunden und verfügt bereits über Treiber im W1-Subsystem. Nach außen geführt wird die One-Wire-Schnittstelle mittels eines RJ-45 Ports. One-Wire-Slaves können mit einem RJ-45 terminierten Netzwerkkabel an diesem angeschlossen werden.

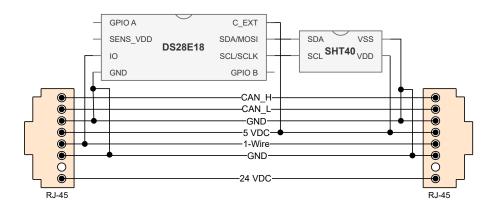

Abbildung 4.1: Sensoreinheit zur Klimadatenerfassung

Für die Sensoreinheit wurde eine Platine entworfen. Diese verfügt über jeweils einen RJ-45 Port an zwei gegenüberliegenden Seiten, welche über Leiterbahnen miteinander verbunden sind. Damit wird es ermöglicht, mehrere Sensoren in Reihe miteinander zu verbinden (Daisy-Chaining). Auf der Platine befinden sich die Bridge von Typ DS28E18 sowie der SHT40 Feuchtigkeits- und Temperatursensor. Beide sind mit den spannungsführenden Leiterbahnen (VDD und GND) verbunden, der DS28E18 zusätzlich mit der One-Wire-Datenleitung. Die Bridge und der Sensor sind über die jeweiligen SDA und SCL Schnittstellen verbunden. Die gesamte Sensorplatine befindet sich in einem Hartplastikgehäuse mit Lufteinlässen, um die Messwerte zuverlässig erfassen zu können und gleichzeitig die Platine vor Beschädigungen zu schützen. Zu beachten ist dabei, dass aufgrund der gewählten Pin-Belegung der RJ-45 Schnittstelle keine Überkreuzkabel verwendet werden

können (siehe Abbildung 4.2).

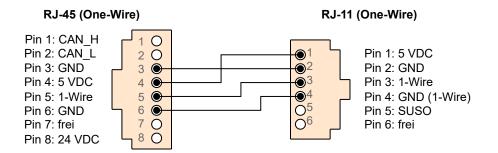

Abbildung 4.2: Anschluss-Schema der One-Wire-Sensorplatine für Klimadatenerfassung

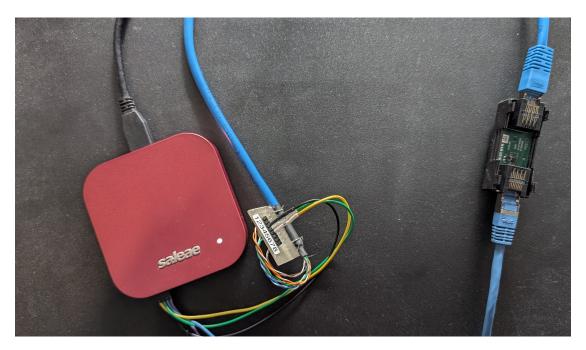

Zur Softwareentwicklung an Desktop-Rechnern wird an Stelle des DS2482S ein Adapter vom Typ DS2490R verwendet. Dieser ist ein USB-Adapter, der als One-Wire-Master agiert. Über einen RJ-11 Port können Slaves mit der One-Wire-Schnittstelle verbunden werden. Da die Sensorplatine über einen RJ-45 Port verfügt, können diese nicht direkt mit dem Adapter verbunden werden. Dazu ist ein spezielles Kabel notwendig, welches über einen RJ-11 Stecker für den DS2490R und einen RJ-45 Stecker für die Sensorplatine besitzt. Dabei ist auf die korrekte Belegung der Pins auf beiden Seiten des Kabels zu achten, wie in Abbildung 4.3 dargestellt. Da die Pinbelegung der Sensorplatine keiner verbreiteten Spezifikation folgt, wird das Adapterkabel individuell angefertigt. Die geschieht durch die Auftrennung von jeweils einem RJ-11 und RJ-45 terminierten Kabel, welche entsprechend der Leiterbelegungen mittels einer Lochstreifenplatte wieder verbunden werden. Da RJ-45 acht und RJ-11 nur sechs Pins besitzt, bleiben dabei zwei Pins des RJ-45 Steckers unbelegt. Weitere zwei Pins bleiben auf beiden Seiten unbelegt, da diese nicht benötigt werden.

### 4.2 Zielstellung

Als Ergebnis dieser Arbeit soll ein Treiber für den DS28E18 entstehen. Dieser führt die Initialisierung der **ROM-ID** automatisch durch, sobald ein Gerät an den Bus angeschlossen wurde. Zur Identifikation dieser Geräte kann der Family Code 0x56 herangezogen werden. Eine Nutzung der grundlegenden I²C-Funktionen des DS28E18 muss ermöglicht werden. Dazu gehört das Schreiben und Auslesen des Sequenzer **SRAM**s, sowie das Ausführen von im Sequenzer gespeicherten

Abbildung 4.3: Steckerbelegung des Speziellen One-Wire-Adapterkabel

Befehlsfolgen. Um die Vorteile des Sequenzers auszunutzen, verfügt der Treiber außerdem über eine optimierte Speicher-Allokationslogik für den **SRAM**. Sofern die angeforderte Operation bereits im Sequenzer programmiert wurde, kann direkt der Befehl zum Ausführen dieser Befehlsfolge gesendet werden.

Um die Nutzerfreundlichkeit zu verbessern soll außerdem die Möglichkeit bestehen, das am DS28E18 verbundene I²C-Gerät über das I2C-Subsystem von Linux anzusteuern. Den Nutzenden ist es so möglich, mit dem Gerät über etablierte Programmierschnittstellen wie i2c-tools zu kommunizieren. Die Treibersoftware abstrahiert die Kommunikation mit dem W1-Subsystem somit weiter und präsentiert den Nutzenden lediglich das Ergebnis der angeforderten Operation. Die Übersetzung der I²C-Befehle in One-Wire-Pakete für den DS28E18 wird gegenüber den Nutzenden abstrahiert.

Daraus ergibt sich die nachfolgend in Punkt 4.1 dargestellte Liste der Anforderungen an den Treiber.

Tabelle 4.1: Anforderungen an den DS28E18 Treiber

- A1. Der Treiber muss die **ROM-ID** Initialisierung implementieren.

- A2. Die **ROM-ID**-Initialisierung muss automatisch beim Verbinden eines Geräts mit dem Bus geschehen.

- A3. Der Treiber muss I<sup>2</sup>C-Lesezugriffe ermöglichen.

- A4. Der Treiber muss I<sup>2</sup>C-Schreibzugriffe ermöglichen.

- A5. Der Treiber muss ein Sequenzer-Speichermanagement implementieren.

- A6. Der Treiber muss bereits im Sequenzer gespeicherte Abläufe nicht erneut programmieren.

- A7. Der Treiber soll den I<sup>2</sup>C-Bus so bereitstellen, dass mittels I2C-Subsystem damit interagiert werden kann.

- A8. Der Treiber soll entsprechenden Code-Style Richtlinien folgen.

- A9. Der Treiber soll parametrierbar sein.

- A10. Der Treiber soll GPIO Interaktionen implementieren.

## 4.3 Abgrenzung

Der DS28E18 kann als Bridge für einen I<sup>2</sup>C- oder SPI-Bus eingesetzt werden. Aufgrund fehlender Hardwareressourcen und der zeitlichen Beschränkung dieser Arbeit wird lediglich ein Treiber für die I<sup>2</sup>C-Schnittstelle entwickelt. Die SPI-Funktionalität findet im Rahmen dieser Arbeit keine weitere Betrachtung.

Der DS28E18 verfügt weiterhin über zwei GPIO-Pins. Im Design der Sensorplatine sind an den GPIO-Pins Widerstände angebracht, welche die Revision der Hardware identifizieren. Die Schnittstelle ist nicht zur Nutzung als GPIO-Pins, etwa zum Anschluss weiterer Sensoren, durch die Nutzenden vorgesehen.

Aus diesem Grund wird der Implementierung im Rahmen dieser Arbeit eine geringe Priorität zugeordnet.

## 4.4 Mögliche Implementierungen

Eine Umsetzung des Treibers ist unter Linux grundlegend auf zwei Weisen möglich: als Implementierung im User-Space oder im Kernel-Space.

Die Implementierung im User-Space ist equivalent zur Entwicklung einer Treiberbibliothek. Dabei werden bereits im Kernel durch das W1-Subsystem bereitgestellte Schnittstellen weiter abstrahiert und die Gerätefunktionen implementiert.

Die Implementierung im Kernel entspricht einer klassischen Treiberentwicklung. Dabei werden hardwarenah Funktionalitäten implementiert, welche gegenüber dem User-Space in einer abstrahierten Schnittstelle präsentiert werden. Über diese können Nutzende und Programme mit dem Treiber, und damit dem Gerät, interagieren.

## 4.4.1 Implementierung im User-Space

Eine User-Space-Implementierung setzt auf dem W1-Subsystem und den darin bereitgestellten Gerätetreibern auf, abstrahiert diese weiter und stellt diese als Bibliothek (Library) bereit. Dabei ist aufgrund des Fehlens eines speziellen Gerätetreibers die Kommunikation nur über den Fallback-Slave-Treiber des Subsystems möglich, welcher die Kommunikation über binären Datenaustausch ermöglicht. Möglich ist diese Interaktion mit Hilfe der Nutzung von  $r_W$ -Dateien oder NETLINK-Sockets, wie bereits in Abbildung 3.1 - W1-Subsystem: Das Kernel One-Wire-Subsystem beschrieben.

Die Bibliothek kann in Software integriert und dort darauf zugegriffen werden. Außerdem ist es möglich zusätzlich eine Anwendung bereitzustellen, welche die Funktionen auf der Befehlszeile bereitstellt.

#### Eigenschaften der User-Space Implementierung

Eine Implementierung im User-Space kann grundlegend in einer beliebigen Programmiersprache erfolgen. Es können dabei gängige Werkzeuge, wie Debugger, verwendet werden, was die Iteration von Softwareversionen vereinfacht. Die Kommunikation mit dem W1-Subsystem kann dabei entweder über Sockets oder rw-Dateien erfolgen. In beiden Fällen kann dies als Lese- und Schreiboperationen auf Dateien implementiert werden.

Diese Form der Implementierung ist grundsätzlich unabhängig von der konkreten Implementierung der Gerätetreiber im Kernel, setzt jedoch definierte Schnittstellen und Abstraktionen zur Kommunikation voraus. Weiterhin ist ein Overhead durch die Kommunikation zwischen User-Space und Kernel-Space und die Interaktion mittels Dateien oder Sockets zu erwarten.

Tabelle 4.2: Vor- und Nachteile: User-Space Implementierung

| Vorteile                             | Nachteile                                   |

|--------------------------------------|---------------------------------------------|

| Programmierung in beliebiger Sprache | Overhead                                    |

| versatile Programmschnittstelle      | auf Kernelabstraktion angewiesen            |

| einfache Iteration und Debugging     | eingeschränkte Interaktion                  |

|                                      | Einbindung als I <sup>2</sup> C-Bus komplex |

## 4.4.2 Implementierung im Kernel

Konzeptionell ist es nicht zielführend, den Sequenzer auszulesen um eine Prüfung programmierter Befehle vorzunehmen. Stattdessen kann der Inhalt des Sequenzers zusätzlich in Kernel-Datenstrukturen abgebildet werden. Durch den Abgleich der I<sup>2</sup>C-Sequenz mit der Datenstruktur direkt im Kernel entfällt die Notwendigkeit, den Sequenzer vorher auszulesen. Damit können One-Wire-Sequenzen gespart werden, was zu einer Zeitersparnis führt.

Aus den genannten Gründen ist daher die Speicherung und der Abgleich in Kernel-Datenstrukturen das Konzept, welches implementiert wird.

## Eigenschaften der Kernel-Implementierung

Da der große Teil des Kernel in C programmiert ist — auch das W1-Subsystem — ist die Wahl der Programmiersprache eingeschränkt. Es existieren Vorstöße etwa zur Programmierung in Rust (siehe [kdcom25]), diese sind jedoch experimentell und für das W1-Subsystem existieren keine Schnittstellenportierungen, sodass eine Implementierung in Rust aus praktischen Gründen nicht in Frage kommt. Da die Verwendung von Debuggern im Kernel sehr umständlich ist, steigt auch der Aufwand für Entwicklung und Iteration der Software. Es bietet sich an, auf andere Methoden zur Fehlersuche wie Log-Ausgaben oder Logic-Analyzer zurückzugreifen.

Gleichzeitig bietet die Implementierung im Kernel einen hohe Grad der Integration in das Betriebssystem, da das Verhalten des Geräts auf Treiber-Ebene gesteuert und angepasst werden kann. So wird es etwa möglich, den I²C-Bus des DS28E18 als solchen im System bereitzustellen. Auch wird so der Zugriff auf das Gerät mittels Kernel-Schnittstellen möglich (wie etwa Netlink, siehe Abbildung 3.1). Weiterhin ist der Overhead dieser Implementierung geringer, da kein wiederholtes Context-Switching notwendig ist und die Ausführung vollständig im Kernel-Space erfolgt, sobald die Daten übermittelt wurden.

Tabelle 4.3: Vor- und Nachteile: Kernel-Implementierung

## Vorteile geringer Overhead hoher Integrationsgrad Einbindung in Kernel-APIs Einbindung als I<sup>2</sup>C-Bus

#### **Nachteile**

Programmierung in C höherer Iterationsaufwand kein Debugger

## 4.5 Bewertung und Schlussfolgerungen

Die Implementierung als Kernel-Treiber stellt ohne Zweifel die robustere Form der Implementierung für den Produktivbetrieb dar. Mit dieser Form wird ermöglicht, auf die Funktionen des Geräts über etablierte Systemschnittstellen wie Sockets aus dem User-Space oder aus weiteren Kernelmodulen zuzugreifen. Die Entwicklung als User-Space-Bibliothek wiederum bietet die Möglichkeit der schnelleren Iteration und vielseitigere Werkzeuge zur Fehlersuche. Diese Implementierung kommt daher auch als Referenzimplementierung in Frage.

In Rücksprache mit den Projektverantwortlichen wird die Entscheidung getroffen, beide Implementierungen zu realisieren. Die User-Space-Bibliothek soll da-

bei lediglich eine grundlegende Kommunikation mit dem DS28E18 ermöglichen und als Referenz für die Treiberentwicklung dienen. Weiterhin soll die Weiterentwicklung der Software für das Steuergerät bereits auf Grundlage der User-Space-Bibliothek durch das Projektteam erfolgen.

Die Entwicklung als Kernel-Treiber stellt das Hauptziel dieser Arbeit dar. Dieser ermöglicht die bessere Integration in das System durch die Bereitstellung von Geräte-Nodes im Verzeichnis /dev mittels **udev**. In der Software des Steuergeräts soll die User-Space-Implementierung langfristig durch den Kernel-Treiber ersetzt werden. Beide Implementierungen, als Kernel-Treiber und User-Space-Bibliothek, werden nach der Entwicklung miteinander verglichen.

## 5. Implementierung im User-Space

Als Referenzimplementierung und um die parallele Weiterentwicklung der Software des Steuergeräts zu ermöglichen, wird zunächst eine Bibliothek für die Verwendung im User-Space angelegt. Da im Projekt, in welchem diese eingegliedert werden soll, bereits Rust eine der dominierenden Sprachen ist, wird auch diese Bibliothek in der Programmiersprache Rust entwickelt. In der späteren Kernel-Treiberentwicklung kann diese Referenzimplementierung dann zum Vergleich der Signale auf dem Bus verwendet werden, um etwaige Fehler in der Protokoll-implementierung ausfindig zu machen.

Zum Lesen und Schreiben auf dem Bus wird der Fallback-Slave-Treiber des W1-Subsystem genutzt, welche über eine rw-Datei Lese- und Schreibzugriff auf den One-Wire-Bus aus dem User-Space zulässt (siehe Abschnitt 3.1 - W1-Subsystem: Das Kernel One-Wire-Subsystem).

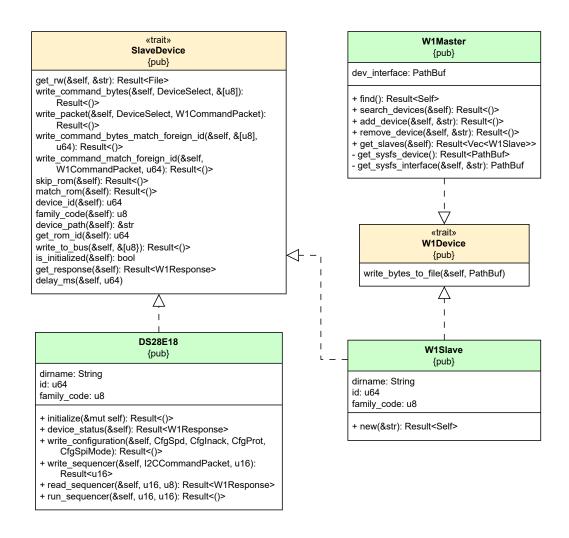

Da sich diese Arbeit auf den DS28E18 konzentriert, ist dieser das einzige speziell implementierte Slave-Gerät (Slave) in der Bibliothek. Jedoch wurde diese so konzipiert und entwickelt, dass eine Erweiterung um weitere Slave-Geräte einfach möglich ist. Dies wurde durch die Verwendung von **Traits** erreicht, um geräteübergreifende Schnittstellen zu definieren.

## 5.1 API Design

Als zentraler **Trait** aller One-Wire-Geräte wird zunächst **trait** W1Device definiert. Dieser stellt zwei Funktionen bereit, welche es ermöglichen einen String **Slice** oder eine Byte **Slice** in eine Datei zu schreiben. Die allgemeinen Implementierungen von Master (W1Master) und Slave (W1Slave) implementieren diesen **Trait** sowie weitere Funktionen. Konkrete Slave-Implementierungen, wie die des DS28E18, bauen auf dieser allgemeinen Implementierung auf und ergänzen diese um gerätespezifische und typspezifische Funktionen.

Eine Übersicht der Typen ist in Abbildung 5.1 zu finden. Rust ist keine objektorientierte Sprache im klassischen Sinne, da Vererbung nicht direkt unterstützt wird. Daher ist eine UML-konforme Abbildung in Klassendiagrammen nicht möglich.

Abbildung 5.1: User-Space Treiber Typen (Ausschnitt, Veranschaulichung)

### 5.1.1 One-Wire-Master

struct W1Master ist die generische Implementierung der Funktionalitäten des One-Wire-Masters der Bibliothek. Da die gerätespezifische Abstraktion bereits im Kernel-Treiber des W1-Subsystems erfolgt, genügt hier eine typspezifische Implementierung.

Die Struktur verfügt als Attribut lediglich über den Pfad des Geräteinterface im **sysfs** (siehe Abbildung 3.1). Die Funktion pub fn find() kann genutzt werden, um eine W1Master-Instanz zu erhalten. Dazu wird im **sysfs** ein entsprechendes Verzeichnis gesucht, welches "master" im Namen trägt.

Die Bibliothek abstrahiert diverse Funktionen, welche bereits durch das W1-Sub-

system bereitgestellt werden. Dazu gehören etwa die Funktionen add\_device und remove\_device, welche die Registrierung oder das Entfernen eines Slave am Master bereitstellen. Dazu wird der vollständige Dateipfad des Slaves im **sysfs** in die entsprechende Datei im **sysfs** geschrieben. Die Funktion search\_device löst eine Suche auf dem One-Wire-Bus aus, indem in die Datei w1\_master\_search der Wert 1 geschrieben wird. Mittels get\_slaves kann ein Vektor aller auf dem Bus vorhandener Slaves erhalten werden. Dazu wird die Datei w1\_master\_slaves ausgelesen, welche alle Slaves auf dem Bus zeilenweise listet. Diese wird ausgelesen und Slave-Instanzen kreiert. Sind keine Slaves verbunden oder noch nicht gefunden, enthält die Datei not found.

```

impl W1Master {

pub fn find() -> Result<Self> {

let dev_interface = Self::get_sysfs_device()?;

trace!("W1Master device: {dev_interface:?}");

4

Ok(Self { dev_interface })

}

fn get_sysfs_device() -> Result<PathBuf> {

std::fs::read_dir(W1_DEV_PATH)

.and_then(|dir_contents| {

10

for entry in dir_contents.flatten() {

11

if entry.file_name().to_string_lossy()

12

.contains("master") {

13

return Ok(entry.path());

14

15

}

16

Err(std::io::Error::new(

17

std::io::ErrorKind::NotFound.

18

"W1 master not found",

19

))

20

})

21

.map_err(anyhow::Error::from)

}

23

```

Quellcode 5.1: User-Space One-Wire-Master Implementierung (Ausschnitt)

Die Implementierung des Masters ist dabei statuslos. Die Instanz verwaltet keine Datenstrukturen des Bus, wie etwa eine Liste der verbundenen Slaves. Sie dient lediglich als Abstraktion zur Interaktion mit dem **sysfs** One-Wire-Master-Interface.

#### 5.1.2 One-Wire-Slaves

Die Implementierung der Slaves erfolgt in Strukturen und **Traits**. Die Struktur struct W1Slave ist ein generischer One-Wire-Slave, welcher wiederum den **Trait** trait SlaveDevice implementiert. Dieser definiert eine allgemeine Programmschnittstelle für alle Slaves. die konkrete Implementierung struct DS28E18 implementiert trait SlaveDevice und beinhaltet W1Slave als Attribut der Struktur und delegiert Zugriffsfunktionen zu dieser Struktur.

#### generische Implementierung: SlaveDevice und W1Slave

Der trait SlaveDevice definiert ein allgemeines Interface für One-Wire-Slaves und die Interaktion mit diesen. Dazu werden Standardimplementierungen von Funktionen zum Schreiben von Daten auf den Bus, sowie für die ROM-Funktionsbefehle SkipRom und MatchRom bereitgestellt. Außerdem definiert der Trait Funktionen zum Auslesen diverser Attribute wie ROM-ID, Gerätepfad und Family Code, sowie zum Lesen der letzten Antwort-Bytes. Diese besitzen keine Standardimplementierung.

Die struct W1Slave bildet einen generischen One-Wire-Slave ab. Dieser implementiert lediglich die **Traits** W1Device und SlaveDevice ohne weitere Logik.

Weiterhin werden die Typen struct W1CommandPacket für One-Wire-Pakete, sowie struct W1Response für Antworten definiert. Diese erlauben eine Datenhaltung für One-Wire-Pakete und Antworten zur weiteren Verwendung.

#### spezifische Implementierung: DS28E18

Der Typ struct DS28E18 implementiert ebenfalls den Trait SlaveDevice. In der Datenstruktur wird außerdem der generische Slave vom Typ W1Slave als Attribut definiert. Die Funktionsimplementierungen des Traits greifen auf diese zu, wie in Ouellcode 5.2 zu sehen.

Weiterhin werden für den DS28E18 gerätespezifische Funktionen implementiert.

## 5.2 Limitierungen

## Overhead durch rw-Datei Implementierung

Die One-Wire-Spezifikation definiert Ausführungszeiten (operation times  $t_{OP}$ ) für alle Operationen auf dem Bus. Diese Angabe entspricht der minimalen Zeit, die

```

pub struct DS28E18 {

1

slave: W1Slave,

2

initialized: bool,

3

4

impl SlaveDevice for DS28E18 {

fn write_to_bus(&self, command: &[u8]) -> Result<()> {

self.slave.write_to_bus(command)

}

8

9

fn device_id(&self) -> u64 {

10

self.slave.id

11

}

13

fn is_initialized(&self) -> bool {

14

self.initialized || self.slave.id != 0

15

16

17

fn get_response(&self) -> Result<W1Response> {

18

self .slave.get_response()

19

20

21

22

}

23

```

Quellcode 5.2: User-Space DS28E18 Implementierung (Ausschnitt)